|

Download Internet Explorer 9. Vista 6. 4Internet Explorer is the world's most popular Web browser. Security, ease of use, and improvements in RSS, CSS, and Ajax support are Microsoft's priorities for Internet Explorer. This version of IE runs on the 6. Windows Vista. The latest version of the browser includes support for. Accelerators - which allow supported web applications to be invoked without explicitly navigating to them. Web. Slices - which allows portions of page to be subscribed to and monitored from a redesigned Favorites Bar. In. Private privacy features. Smart. Screen phishing filter.

For the Intel 6. 4- bit architecture in Itanium chips, see IA- 6. Opteron, the first CPU to introduce the x. It supports vastly larger amounts (theoretically, 2. It is fully backward compatible with 1. Some 6. 4- bit operating systems may no longer be able to support 1. With the upcoming release of Windows 7, the question is raised again on whether you should install the 32-bit version (x86) of the operating system or move up to 64.

Specifically, all 6. Windows are no longer able to execute 1.

Either the 1. 6- bit application must be recompiled to run as a 3. The original specification, created by AMD and released in 2.

AMD, Intel and VIA. The AMD K8 processor was the first to implement the architecture; this was the first significant addition to the x. Intel. Intel was forced to follow suit and introduced a modified Net. Burst family which was fully software- compatible with AMD's design and specification. VIA Technologies introduced x. VIA Isaiah architecture, with the VIA Nano.

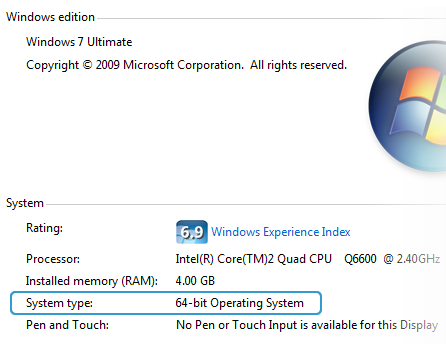

The x. 86- 6. 4 specification is distinct from the Intel Itanium (formerly IA- 6. History. Originally announced in 1. The designers took the opportunity to make other improvements as well. Some of the most significant changes are described below. All general- purpose registers (GPRs) are expanded from 3. Pushes and pops on the stack default to 8- byte strides, and pointers are 8 bytes wide. Additional registers. In addition to increasing the size of the general- purpose registers, the number of named general- purpose registers is increased from eight (i. It is therefore possible to keep more local variables in registers rather than on the stack, and to let registers hold frequently accessed constants; arguments for small and fast subroutines may also be passed in registers to a greater extent. AMD6. 4 still has fewer registers than many common RISCinstruction sets (which typically have 3. However, an AMD6. Additional XMM (SSE) registers. Similarly, the number of 1. XMM registers (used for Streaming SIMD instructions) is also increased from 8 to 1. Larger virtual address space. The AMD6. 4 architecture defines a 6. The architecture definition allows this limit to be raised in future implementations to the full 6. This is compared to just 4 GB (2. The architecture permits extending this to 5. For comparison, 3. GB of RAM in Physical Address Extension (PAE) mode. Any implementation therefore allows the same physical address limit as under long mode. What does 64-bit mean? A CPU or an OS that is 32-bit vs 64-bit refers to the whether it uses data in 32-bit or 64-bit pieces. I have 64-bit Oracle Database Server (11.2.0.3) installed on Windows 2008 R2, and naturally, it automatically installs the 64-bit client. I have to install an. Under Windows 64-bit, 32-bit applications run on top of an emulation of a 32-bit operating system that is called Windows 32-bit on Windows 64-bit, or WOW64 for short. On Windows 7 and Vista, right click on Computer, and click on Properties. On Windows XP, right click on My Computer, and click on Properties.

This makes position independent code, as is often used in shared libraries and code loaded at run time, more efficient. SSE instructions. The original AMD6. Intel's SSE and SSE2 as core instructions. These instruction sets provide a vector supplement to the scalar x. FPU, for the single- precision and double- precision data types. SSE2 also offers integer vector operations, for data types ranging from 8bit to 6. This makes the vector capabilities of the architecture on par with those of the most advanced x. These instructions can also be used in 3. The proliferation of 6. The 3. 2- bit edition of Windows 8, for example, requires the presence of SSE2 instructions. An attempt to execute code from a page tagged . This should make it more difficult for malicious code to take control of the system via . A similar feature has been available on x. Segmented addressing has long been considered an obsolete mode of operation, and all current PC operating systems in effect bypass it, setting all segments to a base address of zero and (in their 3. GB. AMD was the first x. The feature is also available in legacy mode on AMD6. Intel x. 86 processors, when PAE is used. Removal of older features. A few . These include segmented addressing (although the FS and GS segments are retained in vestigial form for use as extra base pointers to operating system structures). These features remain fully implemented in . Some instructions that proved to be rarely useful are not supported in 6. PUSHA/POPA), decimal arithmetic, BOUND and INTO instructions, and . This would be approximately four billion times the size of virtual address space on 3. Most operating systems and applications will not need such a large address space for the foreseeable future, so implementing such wide virtual addresses would simply increase the complexity and cost of address translation with no real benefit. AMD therefore decided that, in the first implementations of the architecture, only the least significant 4. If this requirement is not met, the processor will raise an exception. This is still 6. 5,5. GB address space of 3. This feature eases later scalability to true 6. Many operating systems (including, but not limited to, the Windows NT family) take the higher- addressed half of the address space (named kernel space) for themselves and leave the lower- addressed half (user space) for application code, user mode stacks, heaps, and other data regions. Also, enforcing the . A full mapping hierarchy of 4 KB pages for the whole 4. GB of RAM (about 0. TB virtual space). Operating system limits. Details, where applicable, are given in the . Details on this point are given in the . The x. 87 register stack is not a simple register file although it does allow direct access to individual registers by low cost exchange operations. Also note that 1. GPRs). 1. 6- bit code written for the 8. GPRs, but defaults to using 1. It is used by 6. 4- bit operating systems. Under a 6. 4- bit operating system, 6. Real- mode programs and programs that use virtual 8. This is unlike Intel's IA- 6. However, on the x. SSE2- based FPU support, which a compiler can use for optimization. However, applications that regularly handle integers wider than 3. Legacy mode. In this mode, the processor acts like a 3. Legacy mode allows for a maximum of 3. GB. After several years of denying its existence, Intel announced at the February 2. IDF that the project was indeed underway. Intel's chairman at the time, Craig Barrett, admitted that this was one of their worst- kept secrets. The name used at the IDF was CT (presumably for Clackamas Technology, another codename from an Oregon river); within weeks they began referring to it as IA- 3. IA- 3. 2 extensions) and in March 2. In late 2. 00. 6 Intel began instead using the name Intel 6. AMD's use of the name AMD6. In contrast, the initial Prescott chips (February 2. Intel subsequently began selling Intel 6. Pentium 4s using the E0 revision of the Prescott core, being sold on the OEM market as the Pentium 4, model F. The E0 revision also adds e. Xecute Disable (XD) (Intel's name for the NX bit) to Intel 6. Xeon code- named Irwindale. Intel's official launch of Intel 6. EM6. 4T at that time) in mainstream desktop processors was the N0 stepping Prescott- 2. M. The first Intel mobile processor implementing Intel 6. Merom version of the Core 2 processor, which was released on July 2. None of Intel's earlier notebook CPUs (Core Duo, Pentium M, Celeron M, Mobile Pentium 4) implement Intel 6. Implementations. It is expected that the Isaiah architecture will be twice as fast in integer performance and four times as fast in floating- point performance as the previous- generation VIA Esther at an equivalent clock speed. Power consumption is also expected to be on par with the previous- generation VIA CPUs, with thermal design power ranging from 5 W to 2. W. This is therefore of interest mainly to developers of compilers, operating systems and similar, which must deal with individual and special system instructions. Recent implementations. The processor sets the zero flag and leaves the upper 3. AMD6. 4 requires a different microcode update format and control MSRs (model- specific registers) while Intel 6. Intel 6. 4 lacks some MSRs that are considered architectural in AMD6. These include SYSCFG, TOP. Intel 6. 4 ignores this prefix: the instruction has 3. AMD6. 4 uses 1. 6- bit offset field in the instruction, and clears the top 4. AMD processors raise a floating point Invalid Exception when performing an FLD or FSTP of an 8. Na. N, while Intel processors do not. Intel 6. 4 lacks the ability to save and restore a reduced (and thus faster) version of the floating- point state (involving the FXSAVE and FXRSTOR instructions). Recent AMD6. 4 processors have reintroduced limited support for segmentation, via the Long Mode Segment Limit Enable (LMSLE) bit, to ease virtualization of 6. Similar to CMPXCHG8. B, CMPXCHG1. 6B allows for atomic operations on octal words. This is useful for parallel algorithms that use compare and swap on data larger than the size of a pointer, common in lock- free and wait- free algorithms. Without CMPXCHG1. B one must use workarounds, such as a critical section or alternative lock- free approaches. AMD introduced these instructions (also in 6. Athlon 6. 4, Opteron and Turion 6. D processors in March 2. The 6. 4- bit version of Windows 8. This feature is required by all versions of Windows 8. Early Intel 6. 4 implementations (Prescott and Cedar Mill) only allowed access to 6. GB of physical memory while original AMD6. TB of physical memory. Recent AMD6. 4 implementations provide 2. TB of physical address space (and AMD plans an expansion to 4 PB). Non- CPU architecture co- processors (GPGPU) have also played a big role in performance. Intel's Xeon Phi coprocessors, which implement a subset of x. Development started again during July 2. It was included as a standard distribution architecture as of 5. RELEASE in January 2. Since then, Free. BSD has designated it as a Tier 1 platform. The 6. 0- RELEASE version cleaned up some quirks with running x. Work is currently being done to integrate more fully the x. ABI), in the same manner as the Linux 3. ABI compatibility currently works. Net. BSD source tree on June 1. As of Net. BSD 2. December 9, 2. 00. Net. BSD/amd. 64 is a fully integrated and supported port. The NX bit is used to provide non- executable stack and heap with per- page granularity (segment granularity being used on 3. Open. BSD. Complete in- tree implementation of AMD6. AMD had loaned several machines for the project's hackathon that year. Open. BSD developers have taken to the platform because of its support for the NX bit, which allowed for an easy implementation of the W^X feature. The code for the AMD6.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

November 2017

Categories |

RSS Feed

RSS Feed